Figure 16.23 from Direct-coupled Fet Logic (dcfl) @bullet Source-coupled Fet Logic (scfl) @bullet Advanced Mesfet/hemt Design Examples Iii-v Hbt for Circuit Designers @bullet Current-mode Logic @bullet Emitter-coupled Logic @bullet Ecl/cml Logic Examples @

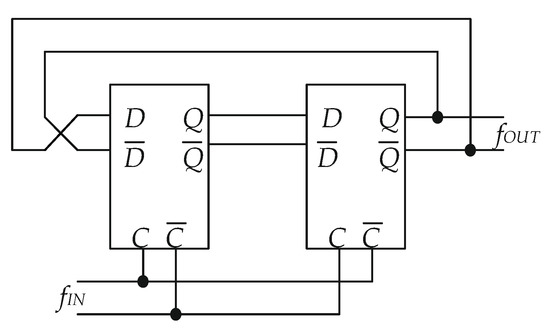

Figure 1 from Design of low-power high-speed dual-modulus frequency divider with improved MOS current mode logic | Semantic Scholar

A Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam Heydari | PDF

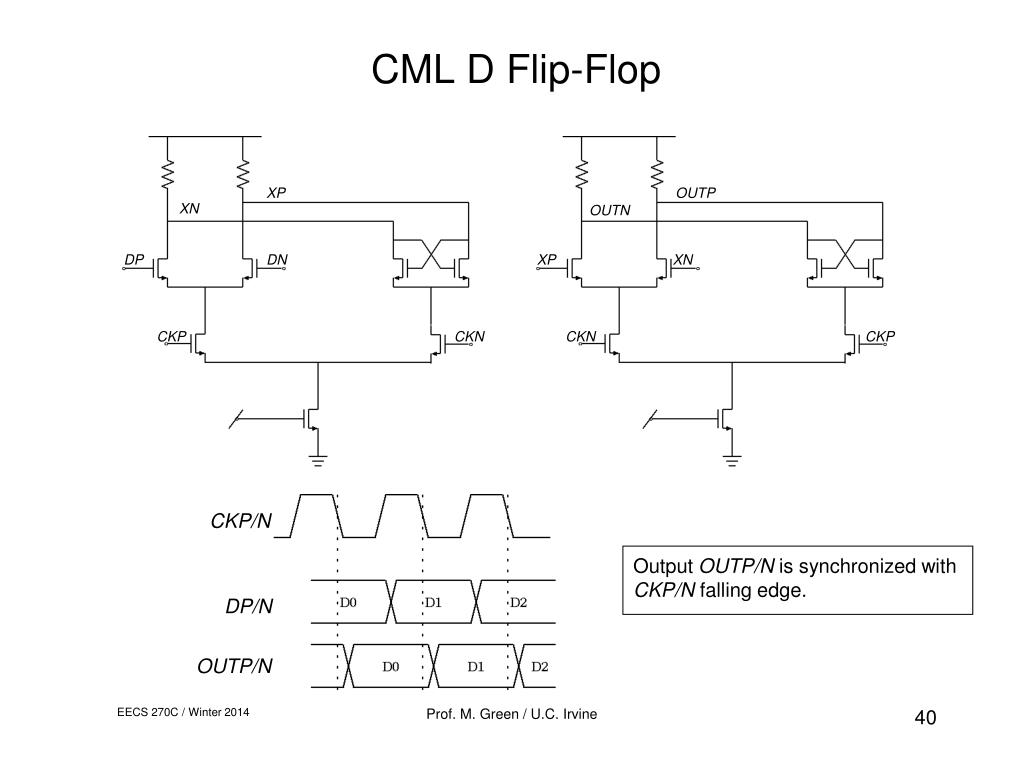

Electronics | Free Full-Text | 40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors

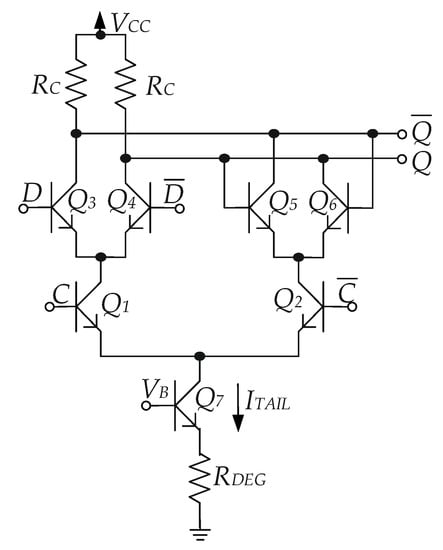

Electronics | Free Full-Text | A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS

Electronics | Free Full-Text | A Power Efficient Frequency Divider With 55 GHz Self-Oscillating Frequency in SiGe BiCMOS